* MUX(Multiplexer) : 다수의 입력을 받아 그 중 하나를 선택해 출력하는 논리 회로

1. 2 - 1 MUX : 2개의 입력을 받아 그 중 하나를 출력으로 선택

1) 진리표

| S0 | A | B | F(out) |

| 0 | 0 | X | 0 |

| 0 | 1 | X | 1 |

| 1 | X | 0 | 0 |

| 1 | X | 1 | 1 |

(간략화 시)

| S0 | F(out) |

| 0 | A |

| 1 | B |

2) 논리식

F = S0b·A + S0·B

3) logic circuit

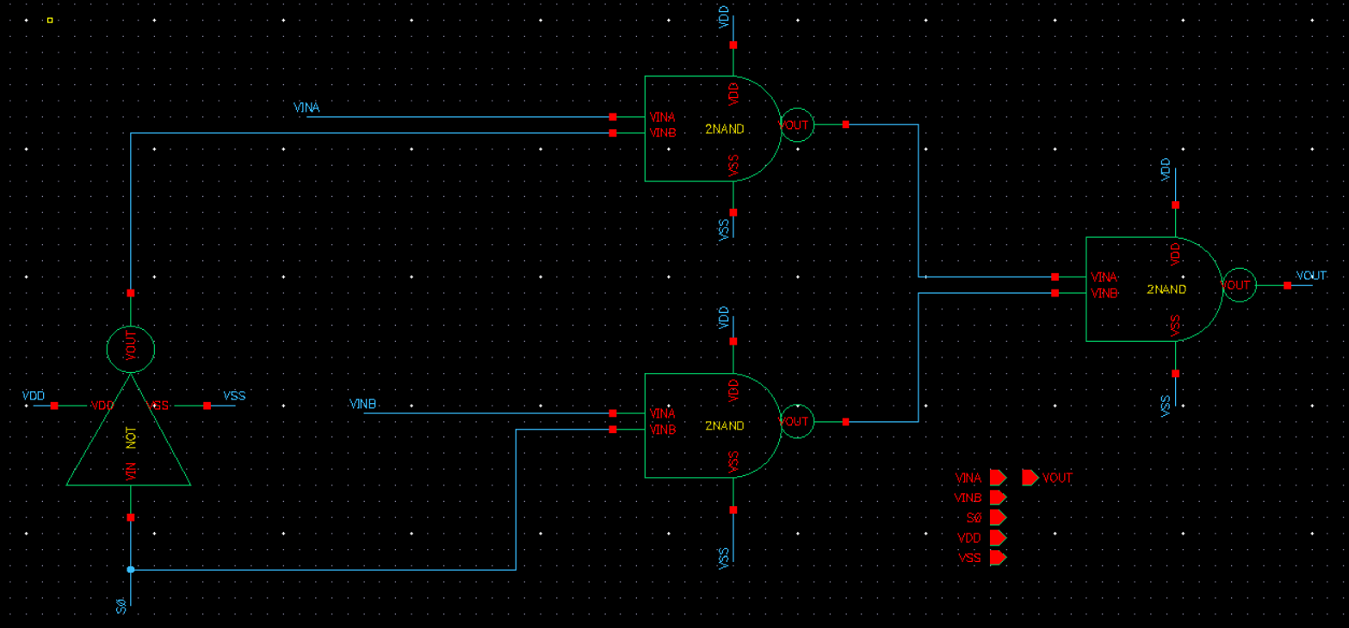

아래 그림과 같이 and / or gate 와 not inverter 사용시 전체 트랜지스터 개수가 20개이지만, nand gate를 사용하는 경우에는 회로 구성에 사용되는 트랜지스터의 개수를 14개로 줄일 수 있다.

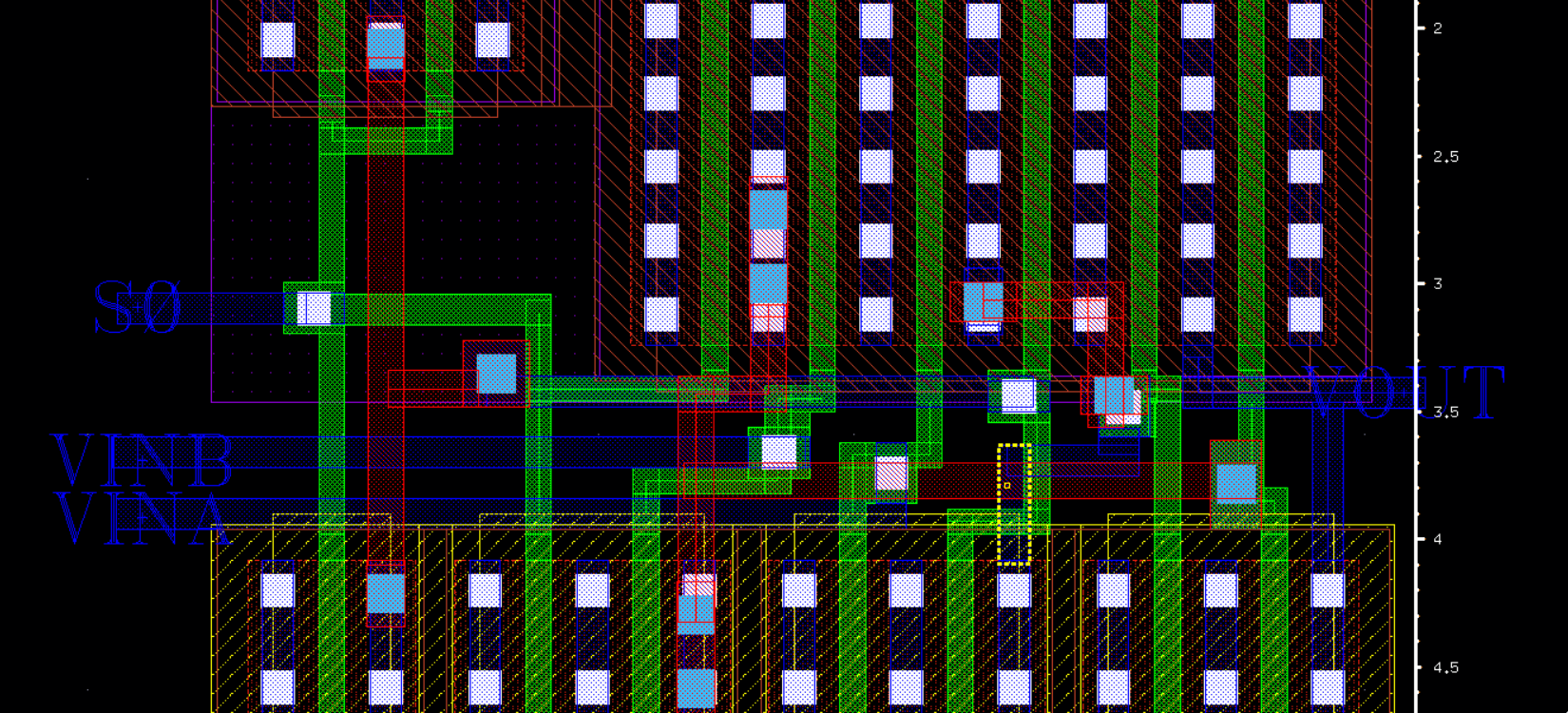

4) layout & stick diagram

- circuit schematic (with 2nand)

- circuit simulation

- layout

2. 2 to 1 MUX (switch 사용)

1) switch

- circuit schematic

- layout

2) 2 to 1 MUX with SWITCH

- circuit schematic

- simulation

- layout

'하만 세미콘 아카데미 8기 > Full Custom One Chip 설계' 카테고리의 다른 글

| Full Custom One Chip Design potfolio (0) | 2024.09.01 |

|---|---|

| 240809 4NAND / 4NOR Gate layout 설계 (0) | 2024.08.09 |

| 240809 - 2 NOR / 3 NOR Gate layout 설계 (0) | 2024.08.09 |

| 240808 2NAND Gate / 3NAND Gate layout 설계 (0) | 2024.08.08 |

| 240807 - 3 input NAND gate / 3 input NOR GATE (0) | 2024.08.07 |