spi (serial peripheral interface) 통신

- 직렬 동기 (synchronous) 방식 -> 1:N (일대다수) 통신 방식, N개만큼의 line이 필요

- 동시에 송수신 가능

- push - pull 방식을 사용함으로써 master와 slave 간 상호 같은 전압을 사용함 → 시그널 정합성과 고속 통신을 지원

- master : 1개, 통신의 시작을 제어, clk 신호를 제공

- slave : 주변장치, 1개 이상

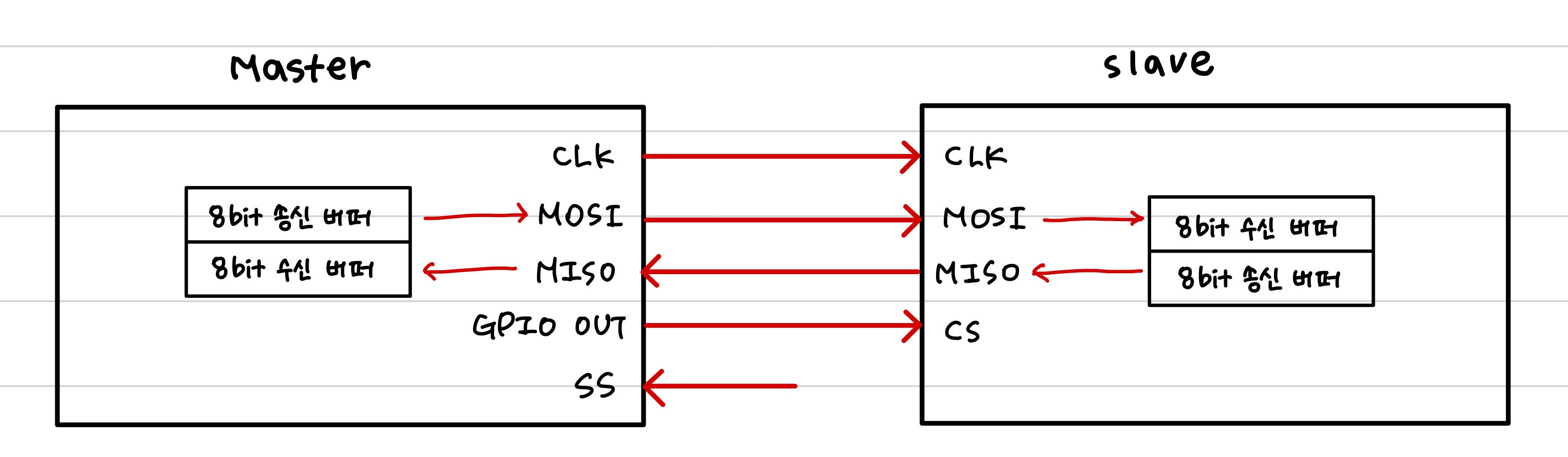

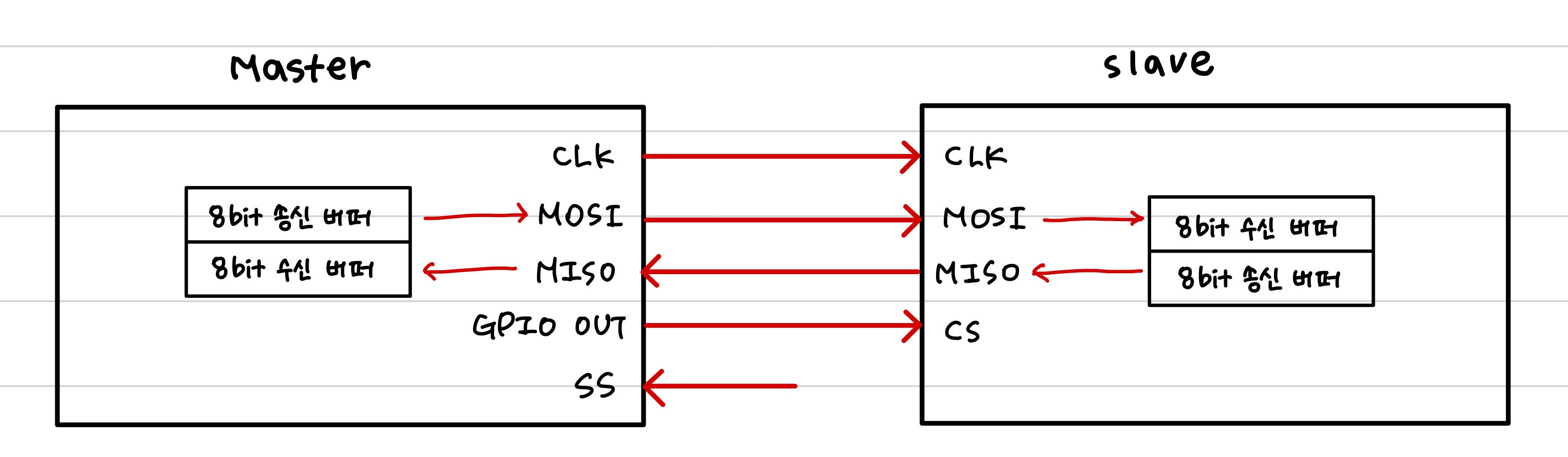

- 신호의 기능

- clk : 데이터에 동기되어 전돨되는 clock 신호, master에서 생성

- MOSI (master out slave in) : clk에 따라 master가 전달하는 data

- MISO (master in slave out) : clk에 따라 slave가 전달하는 데이터

- CS (chip select) : master가 통신을 개시하게 위해 slave를 준비시키는 신호

- SS (slave select) : 멀티 마스터 운영시 다른 spi가 master로 사용됨을 의미

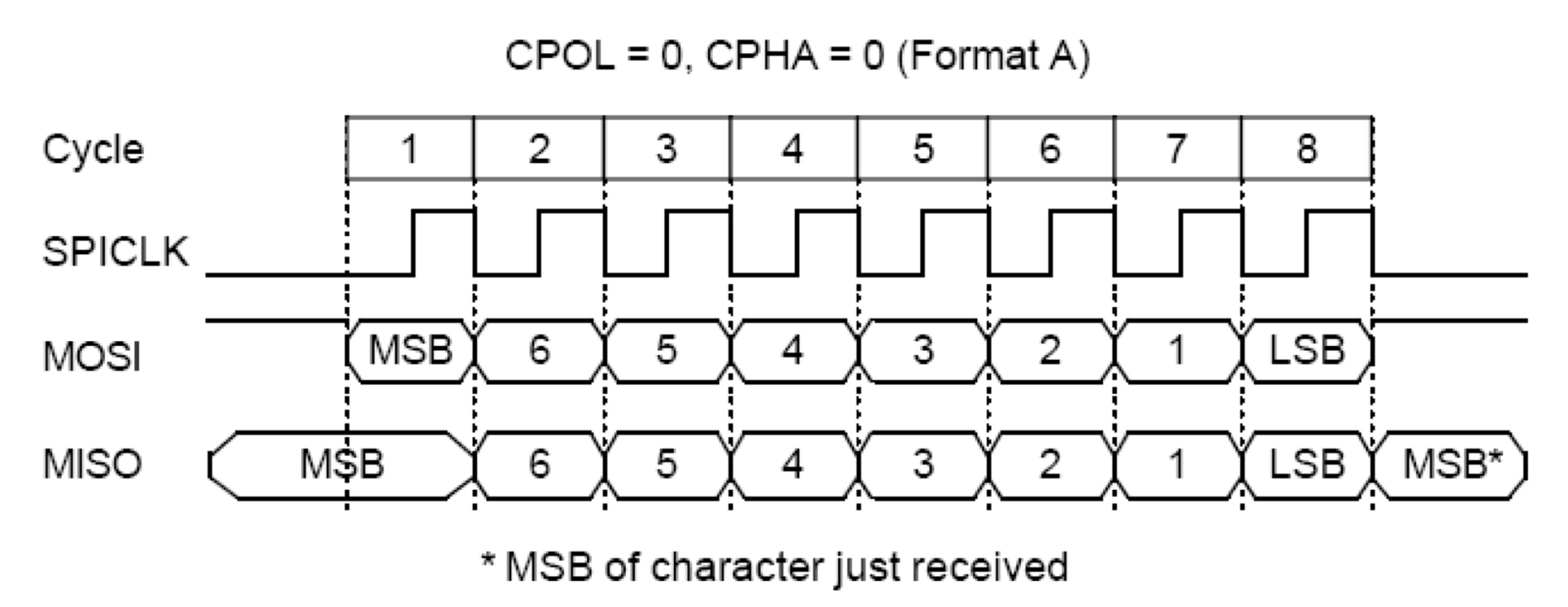

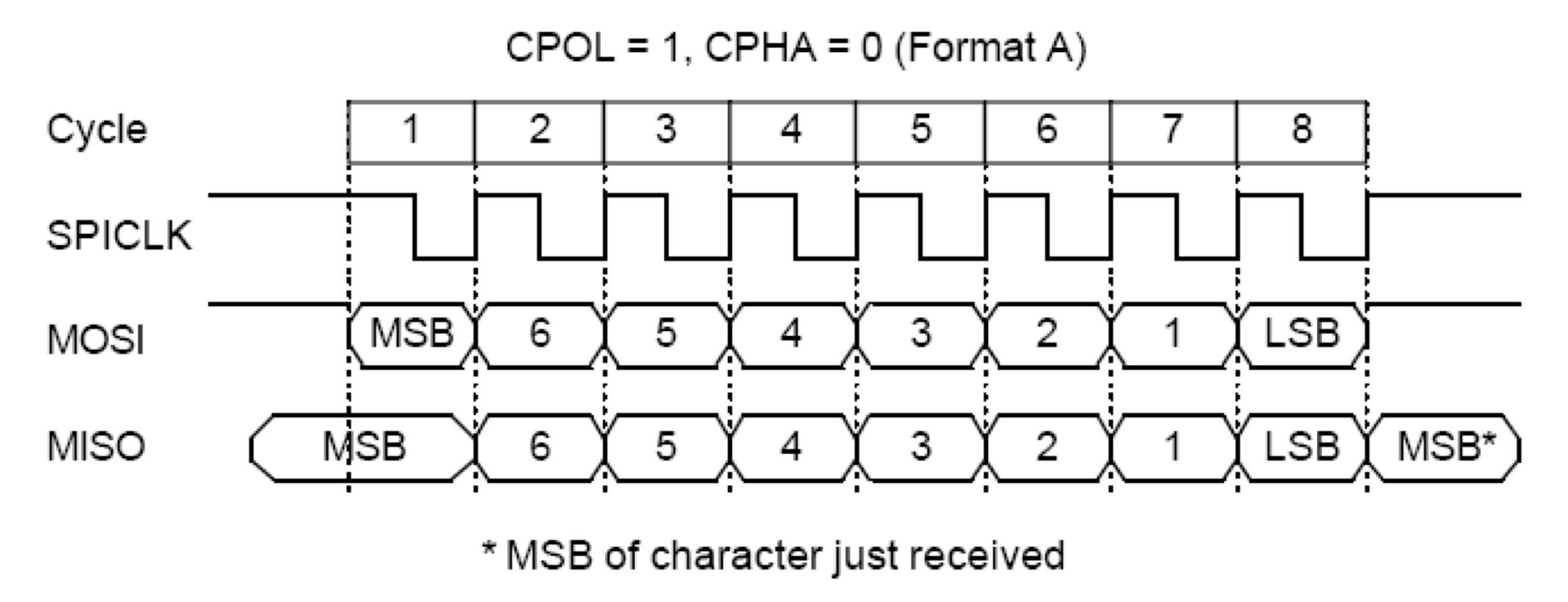

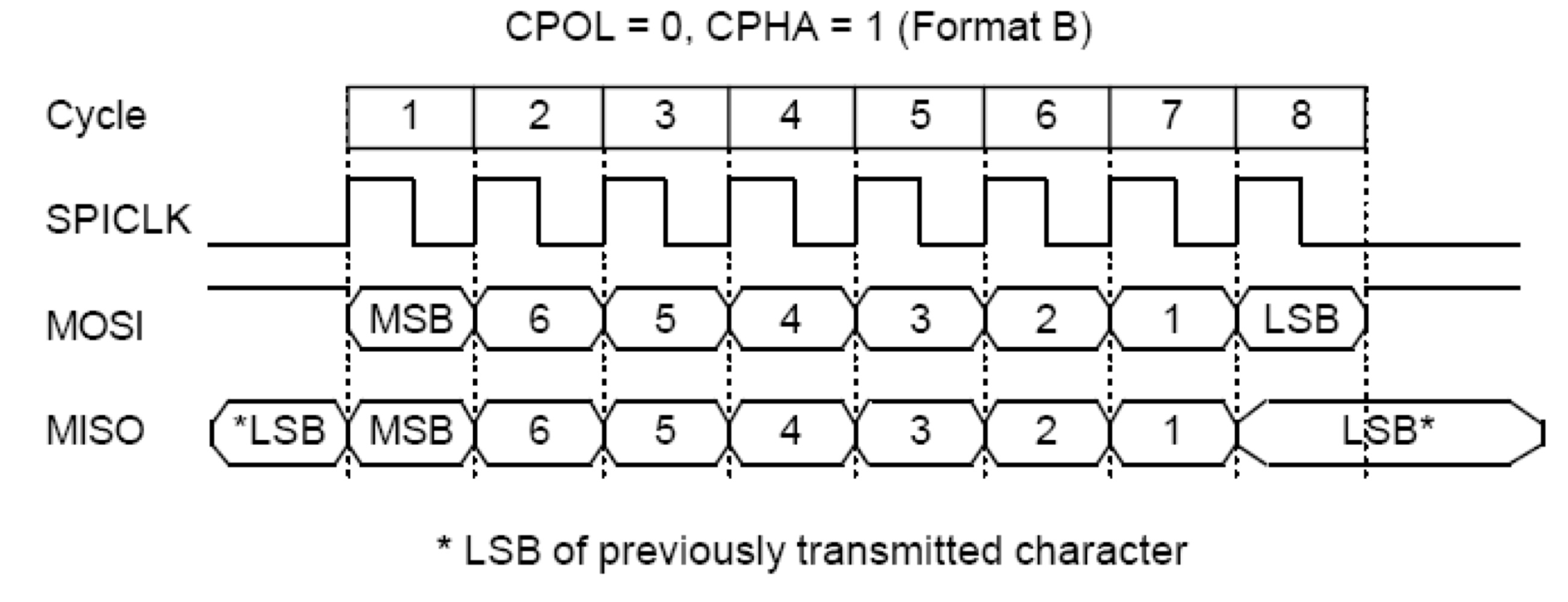

- SPI 통신의 4가지 인터페이스

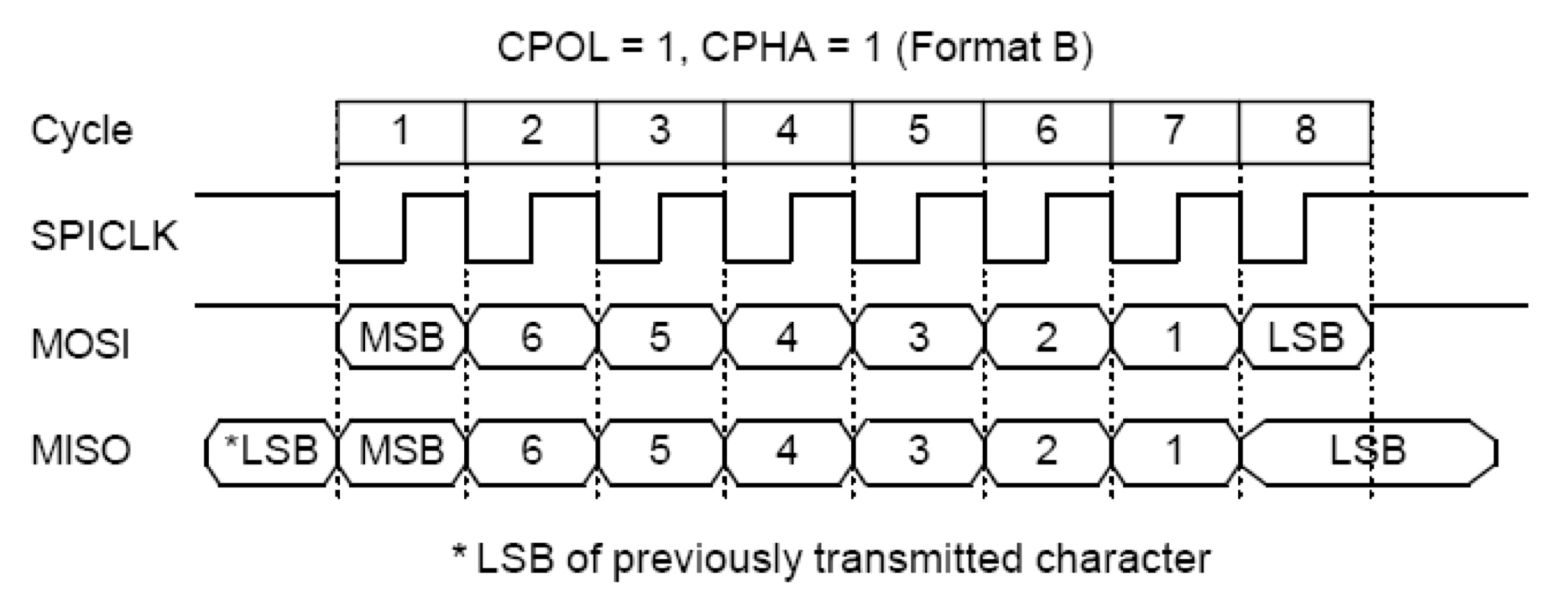

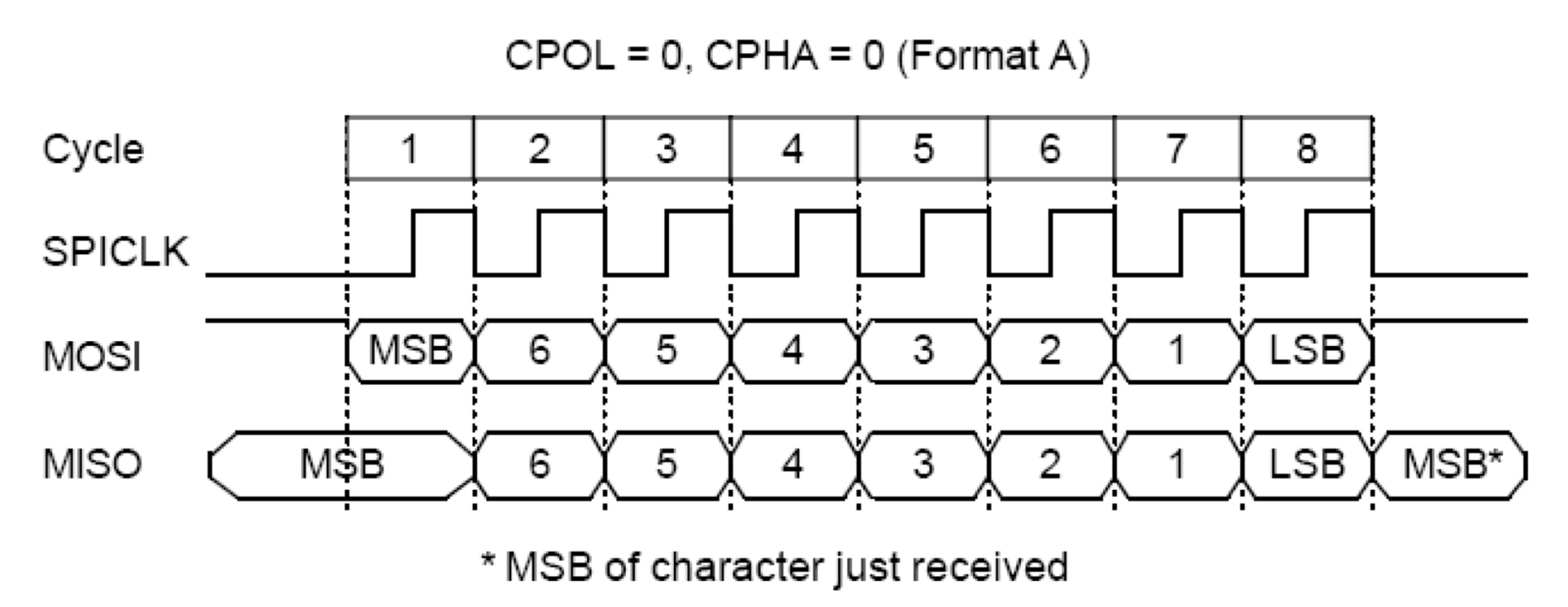

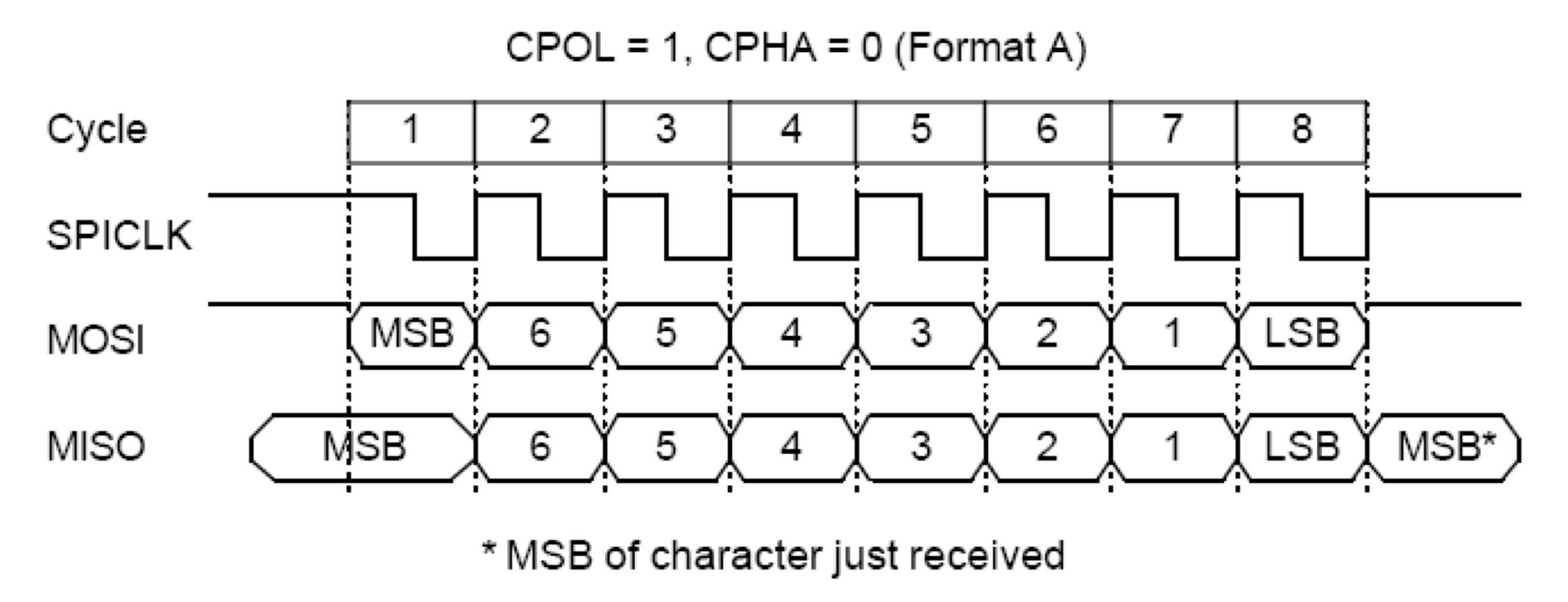

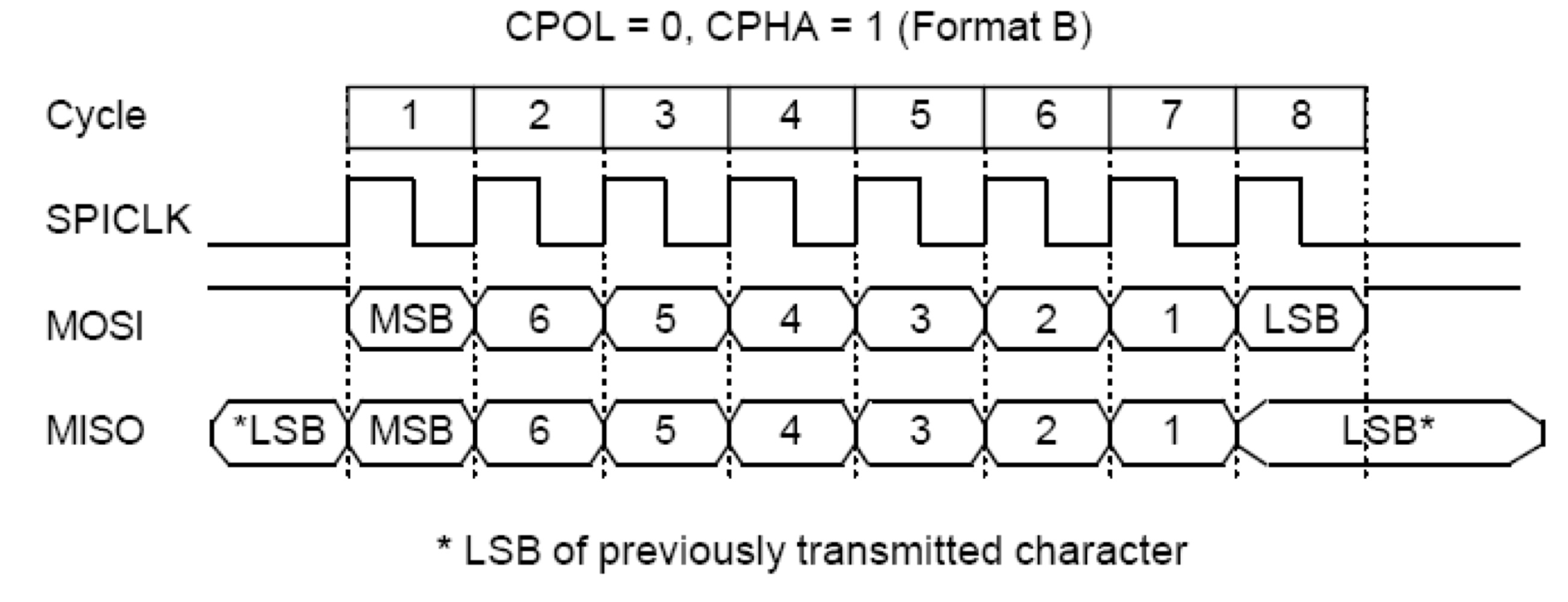

- CPOL : clk 신호의 기본 상태 (idle)에서의 극성을 결정, if IDLE = HIGH → CPOL = 1, IDLE = LOW → CPOL = 0

- CPHA : 데이터의 샘플링 시점을 결정, clk의 첫번째 edge에서 샘플링시 CPHA = 0, 두번째 edge에서 샘플링 시 CPHA = 1

'하만 세미콘 아카데미 8기 > stm32기반 ARM architecture' 카테고리의 다른 글

| stm32f10x GPIO I/O PORT 정리 (+ push-pull/open-drain) (0) | 2024.11.02 |

|---|

spi (serial peripheral interface) 통신

- 직렬 동기 (synchronous) 방식 -> 1:N (일대다수) 통신 방식, N개만큼의 line이 필요

- 동시에 송수신 가능

- push - pull 방식을 사용함으로써 master와 slave 간 상호 같은 전압을 사용함 → 시그널 정합성과 고속 통신을 지원

- master : 1개, 통신의 시작을 제어, clk 신호를 제공

- slave : 주변장치, 1개 이상

- 신호의 기능

- clk : 데이터에 동기되어 전돨되는 clock 신호, master에서 생성

- MOSI (master out slave in) : clk에 따라 master가 전달하는 data

- MISO (master in slave out) : clk에 따라 slave가 전달하는 데이터

- CS (chip select) : master가 통신을 개시하게 위해 slave를 준비시키는 신호

- SS (slave select) : 멀티 마스터 운영시 다른 spi가 master로 사용됨을 의미

- SPI 통신의 4가지 인터페이스

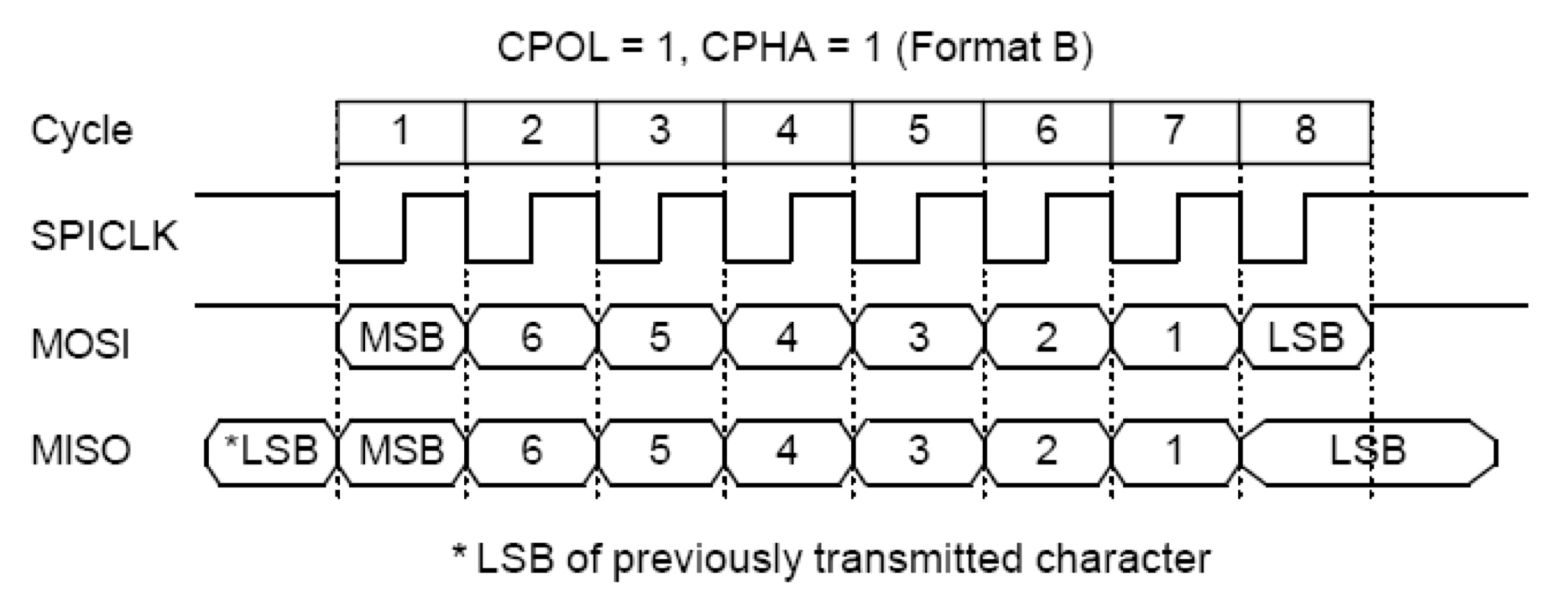

- CPOL : clk 신호의 기본 상태 (idle)에서의 극성을 결정, if IDLE = HIGH → CPOL = 1, IDLE = LOW → CPOL = 0

- CPHA : 데이터의 샘플링 시점을 결정, clk의 첫번째 edge에서 샘플링시 CPHA = 0, 두번째 edge에서 샘플링 시 CPHA = 1

'하만 세미콘 아카데미 8기 > stm32기반 ARM architecture' 카테고리의 다른 글

| stm32f10x GPIO I/O PORT 정리 (+ push-pull/open-drain) (0) | 2024.11.02 |

|---|